#### INTRODUCTION TO BOOLEAN ALGEBRA

Developed for the Azera Group

By: Joseph D. Fournier B.Sc.E.E., M.Sc.E.E.

# Why Study Boolean Algebra?

- Understand the relationship between Boolean logic and digital computer circuits.

- Learn how to design simple logic circuits.

- Understand how digital circuits work together to form complex computer systems.

# **DEFINITION**

- Boolean algebra is a mathematical system for the manipulation of variables that can have one of two values.

- In formal logic, these values are "true" and "false."

- In digital systems, these values are "on" and "off," 1 and 0, or "high" and "low."

- Boolean expressions are created by performing operations on Boolean variables.

- Common Boolean operators include AND, OR, and NOT.

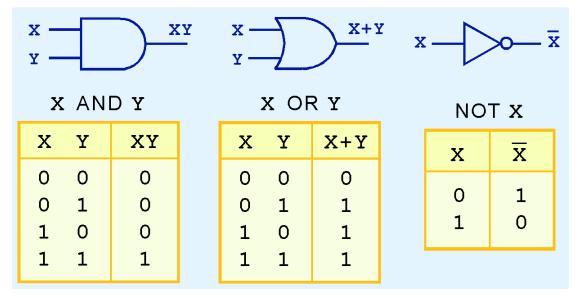

# **Boolean Operators and Truth Tables**

- A Boolean operator can be completely described using a truth table.

- The truth table for the Boolean operators AND and OR are shown at the right.

- The AND operator is also known as a Boolean product. The OR operator is the Boolean sum.

| X | ANI | DΥ |

|---|-----|----|

| X | Y   | XY |

| 0 | 0   | 0  |

| 0 | 1   | 0  |

| 1 | 0   | 0  |

| 1 | 1   | 1  |

| . OI | ` 1              |

|------|------------------|

| Y    | X+Y              |

| 0    | 0                |

| 1    | 1                |

| 0    | 1                |

| 1    | 1                |

|      | Y<br>0<br>1<br>0 |

Y OR V

# **Boolean Operators and Truth Tables: Part Two**

- The truth table for the Boolean NOT operator is shown at the right.

- The NOT operation is most often designated by an overbar. It is sometimes indicated by a prime mark (') or an "elbow" (¬).

| NOT X |                |  |

|-------|----------------|--|

| X     | $\overline{X}$ |  |

| 0     | 1              |  |

| 1     | 0              |  |

#### **Boolean Functions**

- A Boolean function has:

- At least one Boolean variable,

- At least one Boolean operator, and

- At least one input from the set {0,1}.

- It produces an output that is also a member of the set {0,1}.

## **Boolean Functions and Truth Tables**

The truth table for the Boolean function:

$$F(x,y,z) = x\overline{z} + y$$

is shown at the right.

To make evaluation of the Boolean function easier, the truth table contains extra (shaded) columns to hold evaluations of subparts of the function.

| F(X, Y, Z) - XZ+Y |   |   |   |    |                   |

|-------------------|---|---|---|----|-------------------|

| x                 | У | z | z | χΞ | x <del>z</del> +y |

| 0                 | 0 | 0 | 1 | 0  | 0                 |

| 0                 | 0 | 1 | 0 | 0  | 0                 |

| 0                 | 1 | 0 | 1 | 0  | 1                 |

| 0                 | 1 | 1 | 0 | 0  | 1                 |

| 1                 | 0 | 0 | 1 | 1  | 1                 |

| 1                 | 0 | 1 | 0 | 0  | 0                 |

| 1                 | 1 | 0 | 1 | 1  | 1                 |

| 1                 | 1 | 1 | 0 | 0  | 1                 |

$\mathbf{v} = \mathbf{v} = \mathbf{v} = \mathbf{v}$

- As with common arithmetic, Boolean operations have rules of precedence.

- The NOT operator has highest priority, followed by AND and then OR.

- This is how we chose the (shaded) function subparts in our table.

|   | $F(x,y,z) = x\overline{z} + y$ |   |   |    |      |

|---|--------------------------------|---|---|----|------|

| x | У                              | z | z | χZ | xz+y |

| 0 | 0                              | 0 | 1 | 0  | 0    |

| 0 | 0                              | 1 | 0 | 0  | 0    |

| 0 | 1                              | 0 | 1 | 0  | 1    |

| 0 | 1                              | 1 | 0 | 0  | 1    |

| 1 | 0                              | 0 | 1 | 1  | 1    |

| 1 | 0                              | 1 | 0 | 0  | 0    |

| 1 | 1                              | 0 | 1 | 1  | 1    |

| 1 | 1                              | 1 | 0 | 0  | 1    |

# Computer Representations of Boolean Functions

- Digital computers contain circuits that implement Boolean functions.

- The simpler that we can make a Boolean function, the smaller the circuit that will result.

- Simpler circuits are cheaper to build, consume less power, and run faster than complex circuits.

- With this in mind, we always want to reduce our Boolean functions to their simplest form.

- There are a number of Boolean identities that help us to do this.

#### **BOOLEAN IDENTITIES**

Most Boolean identities have an AND (product) form as well as an OR (sum) form. We give our identities using both forms. Our first group is rather intuitive:

| Identity                                         | AND                                            | OR                                                            |

|--------------------------------------------------|------------------------------------------------|---------------------------------------------------------------|

| Name                                             | Form                                           | Form                                                          |

| Identity Law Null Law Idempotent Law Inverse Law | $1x = x$ $0x = 0$ $xx = x$ $x\overline{x} = 0$ | 0 + x = x<br>1 + x = 1<br>x + x = x<br>$x + \overline{x} = 1$ |

# ALGEBRAIC RULES PART ONE

Our second group of Boolean identities should be familiar to you from your study of algebra:

| Identity                                               | AND                                            | OR                                               |

|--------------------------------------------------------|------------------------------------------------|--------------------------------------------------|

| Name                                                   | Form                                           | Form                                             |

| Commutative Law<br>Associative Law<br>Distributive Law | xy = yx $(xy) z = x (yz)$ $x+yz = (x+y) (x+z)$ | x+y = y+x $(x+y)+z = x + (y+z)$ $x(y+z) = xy+xz$ |

# ALGEBRAIC RULES PART TWO

- Our last group of Boolean identities are perhaps the most useful.

- If you have studied set theory or formal logic, these laws are also familiar to you.

| Identity<br>Name                 | AND<br>Form                                                   | OR<br>Form                                                 |

|----------------------------------|---------------------------------------------------------------|------------------------------------------------------------|

| Absorption Law<br>DeMorgan's Law | $x (x+y) = x$ $\overline{(xy)} = \overline{x} + \overline{y}$ | $x + xy = x$ $\overline{(x+y)} = \overline{x}\overline{y}$ |

| Double<br>Complement Law         | ( <u>x</u> )                                                  | = x                                                        |

# **BOOLEAN FUNCTION SIMPLIFICATION**

We can use Boolean identities to simplify the

function:  $F(X,Y,Z) = (X + Y) (X + \overline{Y}) (\overline{XZ})$

as follows:

```

(X + Y) (X + \overline{Y}) (X\overline{Z})

Idempotent Law (Rewriting)

(X + Y) (X + \overline{Y}) (\overline{X} + Z)

DeMorgan's Law

(XX + X\overline{Y} + XY + Y\overline{Y})(\overline{X} + Z)

Distributive Law

((X + Y\overline{Y}) + X(Y + \overline{Y}))(\overline{X} + Z)

Commutative & Distributive Laws

((X + 0) + X(1))(X + Z)

Inverse Law

X(X + Z)

Idempotent Law

XX + XZ

Distributive Law

0 + XZ

Inverse Law

Idempotent Law

XZ

```

#### **DEMORGAN'S LAW: PART ONE**

- Sometimes it is more economical to build a circuit using the complement of a function (and complementing its result) than it is to implement the function directly.

- DeMorgan's law provides an easy way of finding the complement of a Boolean function.

- Recall DeMorgan's law states:

$$\overline{(xy)} = \overline{x} + \overline{y}$$

and  $\overline{(x+y)} = \overline{xy}$

## **DEMORGAN'S LAW: PART TWO**

- DeMorgan's law can be extended to any number of variables.

- Replace each variable by its complement and change all ANDs to ORs and all ORs to ANDs.

- Thus, we find the complement of:

$$F(X,Y,Z) = (XY) + (\overline{X}Z) + (Y\overline{Z})$$

is:

$$\overline{F}(X,Y,Z) = \overline{(XY) + (\overline{XZ}) + (Y\overline{Z})}$$

$$= \overline{(XY)(\overline{XZ})(\overline{YZ})}$$

$$= (\overline{X} + \overline{Y})(X + \overline{Z})(\overline{Y} + Z)$$

# LOGICAL EQUIVALENTS

- Through our exercises in simplifying Boolean expressions, we see that there are numerous ways of stating the same Boolean expression.

- These "synonymous" forms are logically equivalent.

- Logically equivalent expressions have identical truth tables.

- In order to eliminate as much confusion as possible, designers express Boolean functions in standardized or canonical form.

# CANONICAL FORMS OF BOOLEAN EXPRESSIONS: PART ONE

- There are two canonical forms for Boolean expressions: sum-of-products and product-of-sums.

- The Boolean product is the AND operation and the Boolean sum is the OR operation.

- In the sum-of-products form, AND-ed variables are OR-ed together.

- For example: F(x,y,z) = xy + xz + yz

- In the product-of-sums form, OR-ed variables are AND-ed together:

- For example:

$$F(x,y,z) = (x+y)(x+z)(y+z)$$

# CANONICAL FORMS OF BOOLEAN EXPRESSIONS: PART TWO

- To convert a function to sumof-products form use its truth table.

- We are interested in the values of the variables that make the function true (=1).

- Using the truth table, we list the values of the variables that result in a true function value.

- Each group of variables is then OR-ed together.

| F | $F(x,y,z) = x\overline{z} + y$ |   |   |      |  |

|---|--------------------------------|---|---|------|--|

|   | x                              | У | z | xz+y |  |

|   | 0                              | 0 | 0 | 0    |  |

|   | 0                              | 0 | 1 | 0    |  |

| ı | 0                              | 1 | 0 | 1    |  |

| ı | 0                              | 1 | 1 | 1    |  |

|   | 1                              | 0 | 0 | 1    |  |

|   | 1                              | 0 | 1 | 0    |  |

|   | 1                              | 1 | 0 | 1    |  |

|   | 1                              | 1 | 1 | 1    |  |

# CANONICAL FORMS OF BOOLEAN EXPRESSIONS: PART THREE

The sum-of-products form for our function is:

$$F(x,y,z) = \overline{x}y\overline{z} + \overline{x}yz + x\overline{y}\overline{z} + xyz + xyz$$

We note that this function is not in simplest terms. Our aim is only to rewrite our function in canonical sum-of-products form.

$$F(x,y,z) = x\overline{z} + y$$

| x | У | z | xz+y |

|---|---|---|------|

| 0 | 0 | 0 | 0    |

| 0 | 0 | 1 | 0    |

| 0 | 1 | 0 | 1    |

| 0 | 1 | 1 | 1    |

| 1 | 0 | 0 | 1    |

| 1 | 0 | 1 | 0    |

| 1 | 1 | 0 | 1    |

| 1 | 1 | 1 | 1    |

## IMPLEMENTATION OF BOOLEAN FUNCTIONS

- We have looked at Boolean functions in abstract terms.

- In this section, we see that Boolean functions are implemented in digital computer circuits called gates.

- A gate is an electronic device that produces a result based on two or more input values.

- In reality, gates consist of one to six transistors, but digital designers think of them as a single unit.

- Integrated circuits contain collections of gates suited to a particular purpose.

# THREE BASIC LOGIC GATES

The three simplest gates are the AND, OR, and NOT gates.

They correspond directly to their respective Boolean operations, as you can see by their truth tables.

# **EXCLUSIVE OR GATE XOR**

- Another very useful gate is the exclusive OR (XOR) gate.

- The output of the XOR operation is true only when the values of the inputs differ.

|   | <b>x</b> xo | R <b>Y</b>   |                    |

|---|-------------|--------------|--------------------|

| Х | Y           | X $\oplus$ Y |                    |

| 0 | 0           | 0            | х <b>—</b> Д х ө х |

| 0 | 1           | 1            | ·                  |

| 1 | 0           | 1            | - 1 <u> </u>       |

| 1 | 1           | 0            |                    |

Note the special symbol  $\oplus$  for the XOR operation.

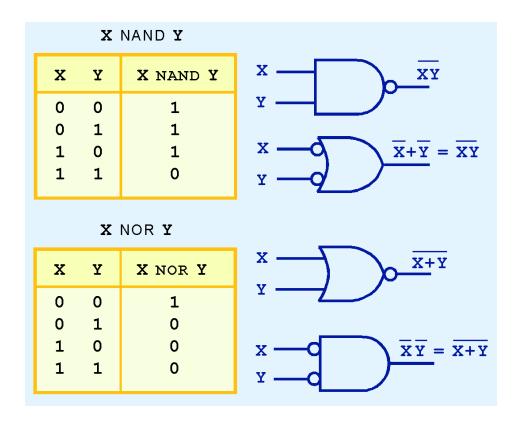

# NAND AND NOR GATES: PART ONE

NAND and NOR

are two very

important gates.

Their symbols and

truth tables are

shown at the right.

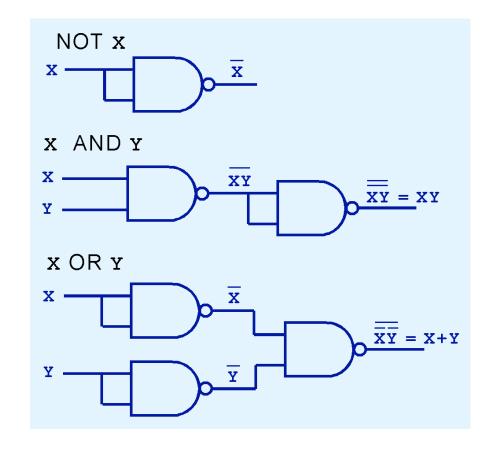

# NAND AND NOR GATES: PART TWO

NAND and NOR are known as universal gates because they are inexpensive to manufacture and any Boolean function can be constructed using only NAND or only NOR gates.

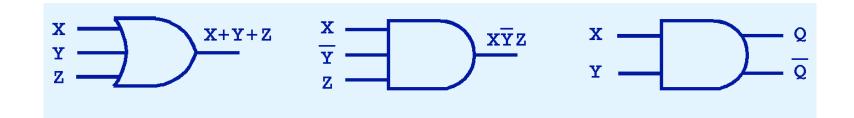

# FEATURES OF LOGIC GATES: PART ONE

- Gates can have multiple inputs and more than one output.

- A second output can be provided for the complement of the operation.

- We'll see more of this later.

## FEATURES OF LOGIC GATES: PART TWO

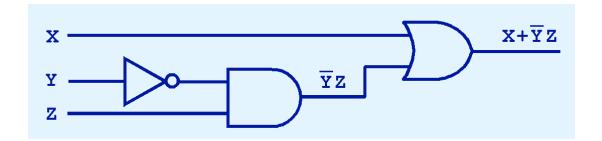

- The main thing to remember is that combinations of gates implement Boolean functions.

- The circuit below implements the Boolean

function:

$$F(X,Y,Z) = X + \overline{Y}Z$$

We simplify our Boolean expressions so that we can create simpler circuits.

#### COMBINATIONAL LOGIC CIRCUIT GATES: ONE

We have designed a circuit that implements the Boolean function:

$$F(X,Y,Z) = X + \overline{Y}Z$$

- This circuit is an example of a combinational logic circuit.

- Combinational logic circuits produce a specified output (almost) at the instant when input values are applied.

- In a later section, we will explore circuits where this is not the case.

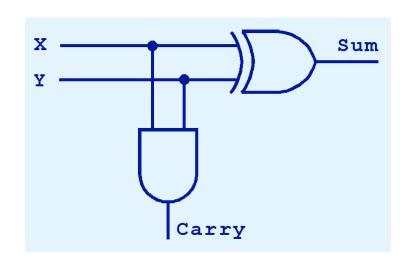

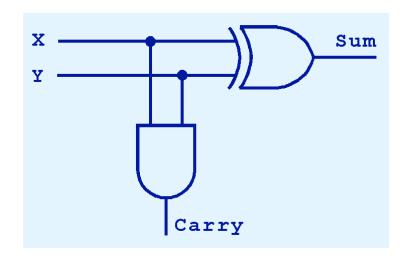

#### LOGIC CIRCUIT: HALF ADDER PART ONE

- Combinational logic circuits give us many useful devices.

- One of the simplest is the half adder, which finds the sum of two bits.

- We can gain some insight as to the construction of a half adder by looking at its truth table, shown at the right.

| Inp | uts | Out | tputs |

|-----|-----|-----|-------|

| X   | Y   | Sum | Carry |

| 0   | 0   | 0   | 0     |

| 0   | 1   | 1   | 0     |

| 1   | 0   | 1   | 0     |

| 1   | 1   | 0   | 1     |

#### LOGIC CIRCUIT: HALF ADDER PART TWO

As we see, the sum can be found using the XOR operation and the carry using the AND operation.

| Inputs |   | Outputs |       |  |

|--------|---|---------|-------|--|

| Х      | Y | Sum     | Carry |  |

| 0      | 0 | 0       | 0     |  |

| 0      | 1 | 1       | 0     |  |

| 1      | 0 | 1       | 0     |  |

| 1      | 1 | 0       | 1     |  |

## LOGIC CIRCUIT: HALF ADDER PART THREE

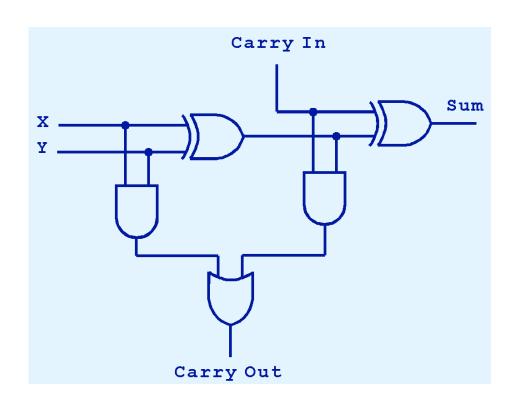

- We can change our half adder into to a full adder by including gates for processing the carry bit.

- The truth table for a full adder is shown at the right.

| Inputs |   |             | Outputs |              |  |

|--------|---|-------------|---------|--------------|--|

| x      | Y | Carry<br>In | Sum     | Carry<br>Out |  |

| 0      | 0 | 0           | 0       | 0            |  |

| 0      | 0 | 1           | 1       | 0            |  |

| 0      | 1 | 0           | 1       | 0            |  |

| 0      | 1 | 1           | 0       | 1            |  |

| 1      | 0 | 0           | 1       | 0            |  |

| 1      | 0 | 1           | 0       | 1            |  |

| 1      | 1 | 0           | 0       | 1            |  |

| 1      | 1 | 1           | 1       | 1            |  |

# LOGIC CIRCUIT: FULL ADDER PART ONE

How can we change the half adder shown below to make it a full adder?

| Inputs |               |   | Outputs          |   |  |

|--------|---------------|---|------------------|---|--|

| х      | Carry<br>Y In |   | Carry<br>Sum Out |   |  |

| 0      | 0             | 0 | 0                | 0 |  |

| 0      | 0             | 1 | 1                | 0 |  |

| 0      | 1             | 0 | 1                | 0 |  |

| 0      | 1             | 1 | 0                | 1 |  |

| 1      | 0             | 0 | 1                | 0 |  |

| 1      | 0             | 1 | 0                | 1 |  |

| 1      | 1             | 0 | 0                | 1 |  |

| 1      | 1             | 1 | 1                | 1 |  |

# 4

# LOGIC CIRCUIT: FULL ADDER PART TWO

Here's our completed full adder.

|   | Inp | uts         | Outputs |              |  |

|---|-----|-------------|---------|--------------|--|

| X | Y   | Carry<br>In | Sum     | Carry<br>Out |  |

| 0 | 0   | 0           | 0       | 0            |  |

| 0 | 0   | 1           | 1       | 0            |  |

| 0 | 1   | 0           | 1       | 0            |  |

| 0 | 1   | 1           | 0       | 1            |  |

| 1 | 0   | 0           | 1       | 0            |  |

| 1 | 0   | 1           | 0       | 1            |  |

| 1 | 1   | 0           | 0       | 1            |  |

| 1 | 1   | 1           | 1       | 1            |  |

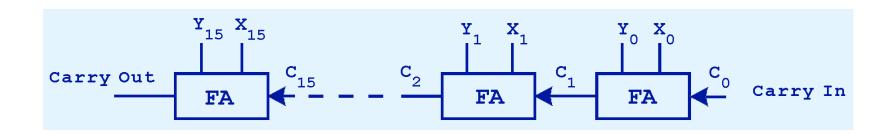

#### LOGIC CIRCUIT: RIPPLE-CARRY ADDER

- Just as we combined half adders to make a full adder, full adders can connected in series.

- The carry bit "ripples" from one adder to the next; hence, this configuration is called a *ripple-carry* adder.

Today's systems employ more efficient adders.

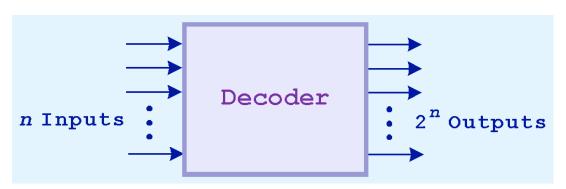

#### LOGIC CIRCUIT: DECODER: PART ONE

- Decoders are another important type of combinational circuit.

- Among other things, they are useful in selecting a memory location according a binary value placed on the address lines of a memory bus.

- Address decoders with n inputs can select any of 2<sup>n</sup> locations.

This is a block diagram for a decoder.

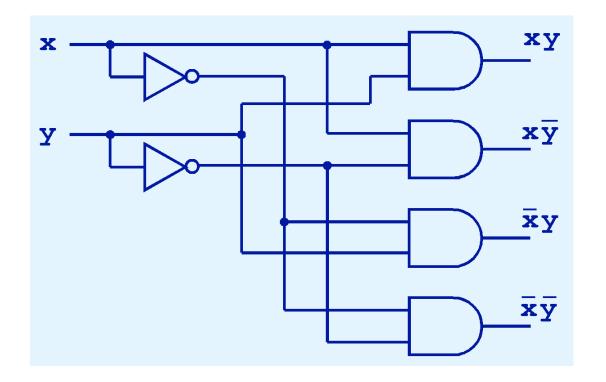

# LOGIC CIRCUIT: DECODER: PART TWO

This is what a 2-to-4 decoder looks like on the inside.

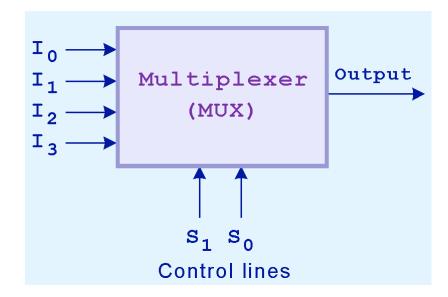

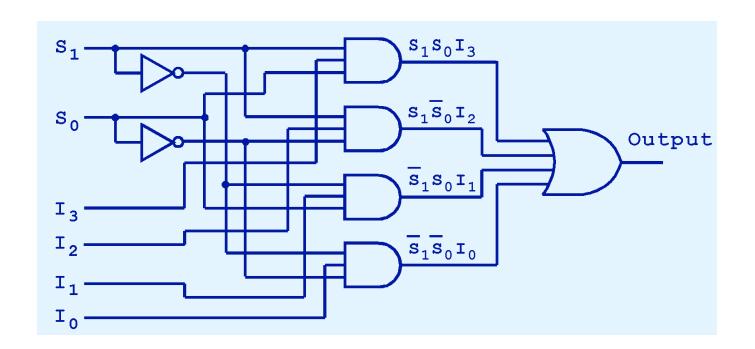

#### LOGIC CIRCUIT: MULTIPLEXER: PART ONE

- A multiplexer does just the opposite of a decoder.

- It selects a single output from several inputs.

- The particular input chosen for output is determined by the value of the multiplexer's control lines.

- To be able to select among *n* inputs, log<sub>2</sub>*n* control lines are needed.

This is a block diagram for a multiplexer.

# LOGIC CIRCUIT: MULTIPLEXER: PART TWO

This is what a 4-to-1 multiplexer looks like on the inside.

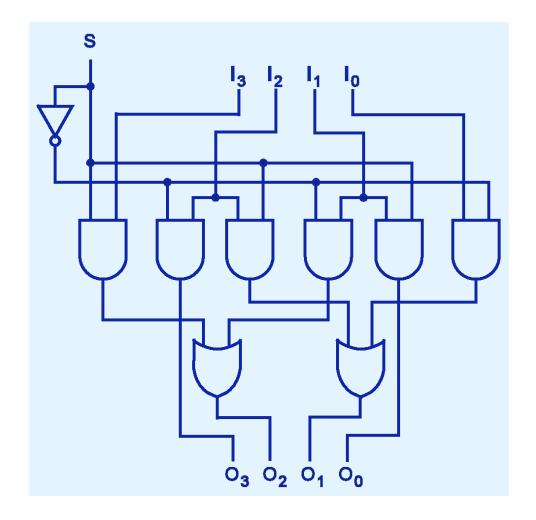

# LOGIC CIRCUIT: SHIFTER

This shifter moves the bits of a nibble one position to the left or right.

#### SEQUENTIAL LOGIC CIRCUITS: PART ONE

- Combinational logic circuits are perfect for situations when we require the immediate application of a Boolean function to a set of inputs.

- There are other times, however, when we need a circuit to change its value with consideration to its current state as well as its inputs.

- These circuits have to "remember" their current state.

- Sequential logic circuits provide this functionality for us.

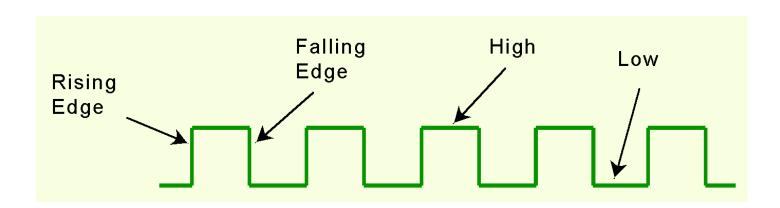

#### SEQUENTIAL LOGIC CIRCUITS: PART TWO

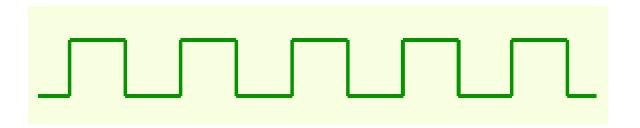

- As the name implies, sequential logic circuits require a means by which events can be sequenced.

- State changes are controlled by clocks.

- A "clock" is a special circuit that sends electrical pulses through a circuit.

- Clocks produce electrical waveforms such as the one shown below.

#### SEQUENTIAL LOGIC CIRCUITS: PART THREE

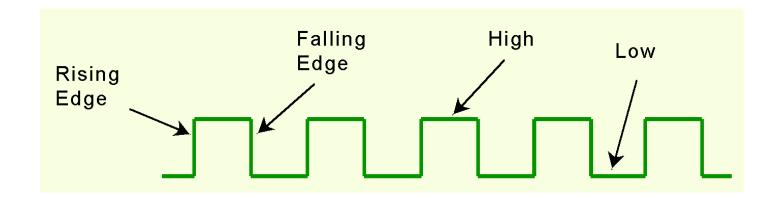

- State changes occur in sequential circuits only when the clock ticks.

- Circuits can change state on the rising edge, falling edge, or when the clock pulse reaches its highest voltage.

#### SEQUENTIAL LOGIC CIRCUITS: PART FOUR

- Circuits that change state on the rising edge, or falling edge of the clock pulse are called edgetriggered.

- Level-triggered circuits change state when the clock voltage reaches its highest or lowest level.

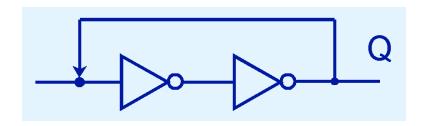

### LOGIC CIRCUITS: FEEDBACK PART ONE

- To retain their state values, sequential circuits rely on feedback.

- Feedback in digital circuits occurs when an output is looped back to the input.

- A simple example of this concept is shown below.

- If Q is 0 it will always be 0, if it is 1, it will always be 1. Why?

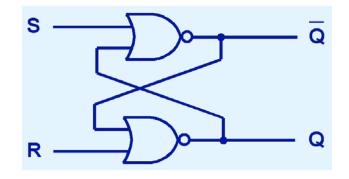

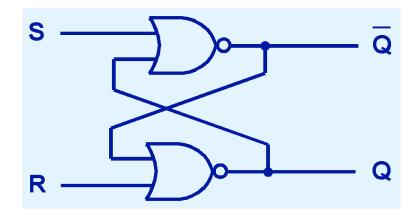

# LOGIC CIRCUITS: SET/RESET FLIP-FLOP PART ONE

- You can see how feedback works by examining the most basic sequential logic components, the SR flip-flop.

- The "SR" stands for set/reset.

- The internals of an SR flip-flop are shown below, along with its block diagram.

# LOGIC CIRCUITS: SET/RESET FLIP-FLOP PART TWO

- The behavior of an SR flip-flop is described by a characteristic table.

- Q(t) means the value of the output at time t.

Q(t+1) is the value of Q after the next clock pulse.

| s | R | Q(t+1)           |

|---|---|------------------|

| 0 | 0 | Q(t) (no change) |

| 0 | 1 | 0 (reset to 0)   |

| 1 | 0 | 1 (set to 1)     |

| 1 | 1 | undefined        |

|   |   |                  |

# LOGIC CIRCUITS: SET/RESET FLIP-FLOP PART THREE

- The SR flip-flop actually has three inputs: S, R, and its current output, Q.

- Thus, we can construct a truth table for this circuit, as shown at the right.

- Notice the two undefined values. When both S and R are 1, the SR flipflop is unstable.

|   | Present<br>State |      | Next<br>State |

|---|------------------|------|---------------|

| S | R                | Q(t) | Q(t+1)        |

| 0 | 0                | 0    | O             |

| 0 | 0                | 1    | 1             |

| 0 | 1                | 0    | 0             |

| 0 | 1                | 1    | 0             |

| 1 | 0                | 0    | 1             |

| 1 | 0                | 1    | 1             |

| 1 | 1                | 0    | undefined     |

| 1 | 1                | 1    | undefined     |

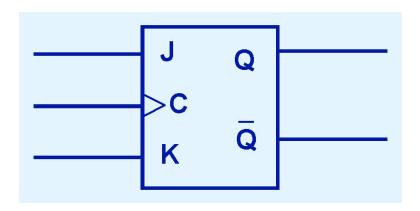

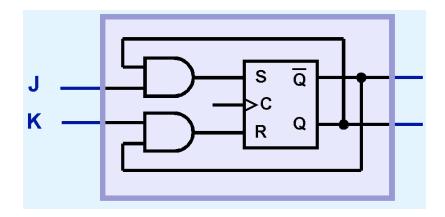

### LOGIC CIRCUITS: JK FLIP-FLOP PART ONE

- If we can be sure that the inputs to an SR flip-flop will never both be 1, we will never have an unstable circuit. This may not always be the case.

- The SR flip-flop can be modified to provide a stable state when both inputs are 1.

- This modified flip-flop is called a JK flip-flop, shown at the right.

#### LOGIC CIRCUITS: JK FLIP-FLOP PART TWO

- At the right, we see how an SR flip-flop can be modified to create a JK flip-flop.

- The characteristic table indicates that the flip-flop is stable for all inputs.

| J K                      | Q(t+1)                                            |

|--------------------------|---------------------------------------------------|

| 0 0<br>0 1<br>1 0<br>1 1 | Q(t) (no change) 0 (reset to 0) 1 (set to 1) Q(t) |

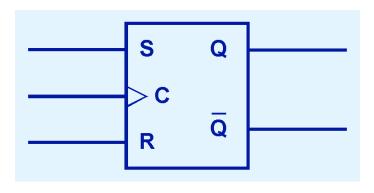

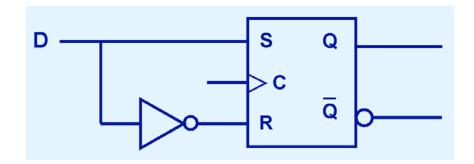

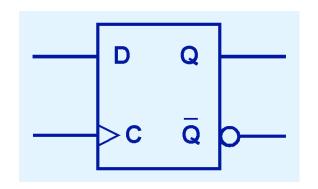

### LOGIC CIRCUITS: D FLIP-FLOP PART ONE

- Another modification of the SR flip-flop is the D flip-flop, shown below with its characteristic table.

- You will notice that the output of the flip-flop remains the same during subsequent clock pulses. The output changes only when the value of D changes.

| D | Q(t+1) |

|---|--------|

| 0 | 0      |

| 1 | 1      |

### LOGIC CIRCUITS: D FLIP-FLOP PART TWO

- The D flip-flop is the fundamental circuit of computer memory.

- D flip-flops are usually illustrated using the block diagram shown below.

- The characteristic table for the D flip-flop is shown at the right.

| D | Q(t+1) |

|---|--------|

| 0 | 0      |

| 1 | 1      |

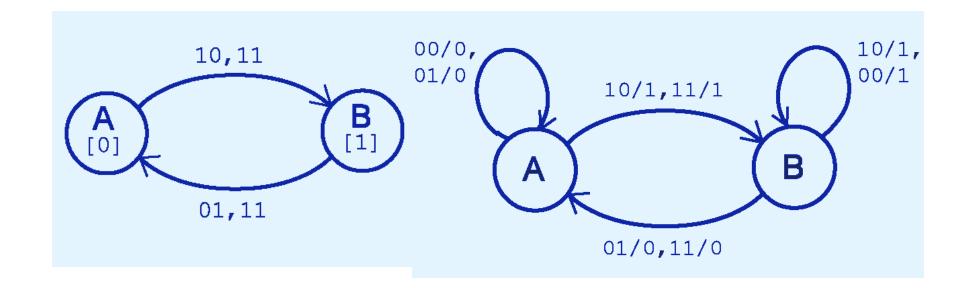

### FINITE STATE MACHINES: PART ONE

- The behavior of sequential circuits can be expressed using characteristic tables or finite state machines (FSMs).

- FSMs consist of a set of nodes that hold the states of the machine and a set of arcs that connect the states.

- Moore and Mealy machines are two types of FSMs that are equivalent.

- They differ only in how they express the outputs of the machine.

- Moore machines place outputs on each node, while

Mealy machines present their outputs on the transitions.

#### FINITE STATE MACHINES: PART TWO

The behavior of a JK flop-flop is depicted below by a Moore machine (left) and a Mealy machine (right).

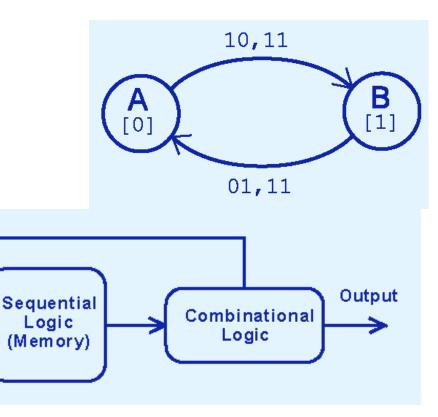

### FINITE STATE MACHINES: MOORE MACHINE

Although the behavior of Moore and Mealy machines is identical, their implementations differ.

This is our Moore machine.

Combinational

Logic

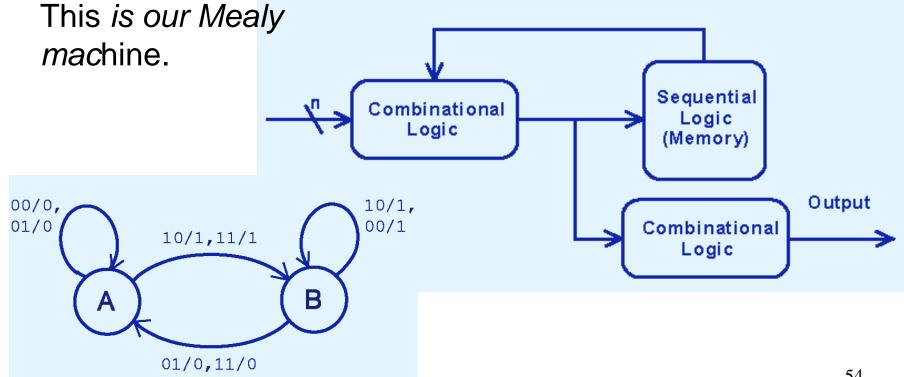

#### FINITE STATE MACHINES: MEALY MACHINE

Although the behavior of Moore and Mealy machines is identical, their implementations differ.

54

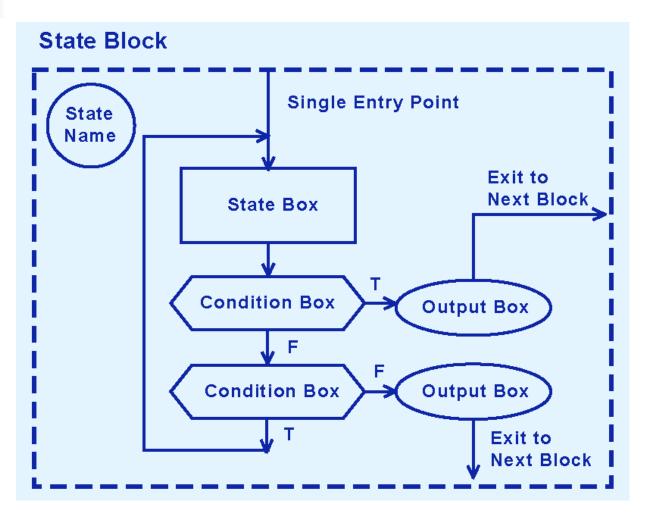

#### ALGORITHMIC STATE MACHINES: PART ONE

- It is difficult to express the complexities of actual implementations using only Moore and Mealy machines.

- For one thing, they do not address the intricacies of timing very well.

- Secondly, it is often the case that an interaction of numerous signals is required to advance a machine from one state to the next.

- For these reasons, Christopher Clare invented the algorithmic state machine (ASM).

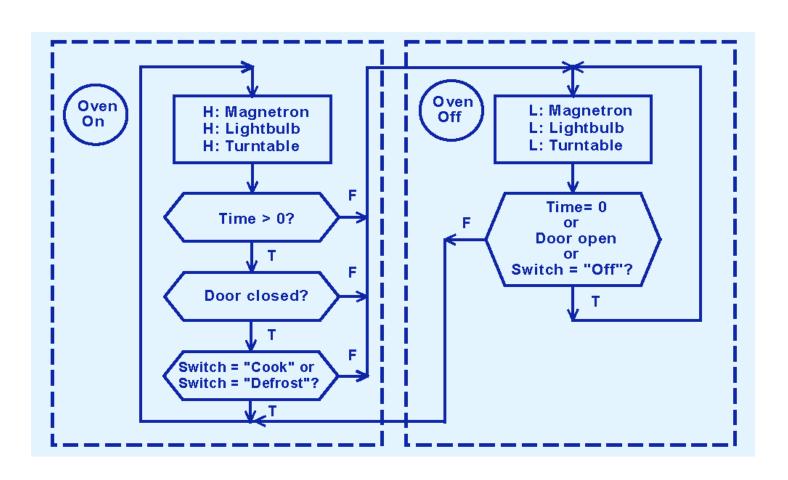

# ALGORITHMIC STATE MACHINE: PART TWO

# THE ASM for a microwave oven.

# SEQUENTIAL CIRCUITS: PART ONE

- Sequential circuits are used anytime that we have a "stateful" application.

- A stateful application is one where the next state of the machine depends on the current state of the machine and the input.

- A stateful application requires both combinational and sequential logic.

- The following slides provide several examples of circuits that fall into this category.

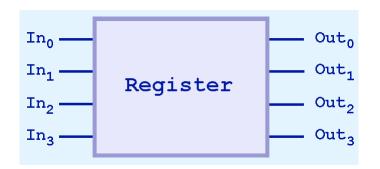

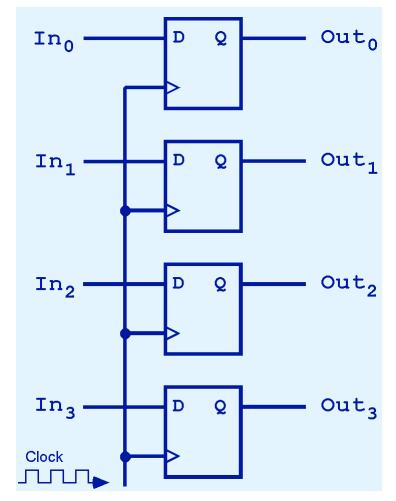

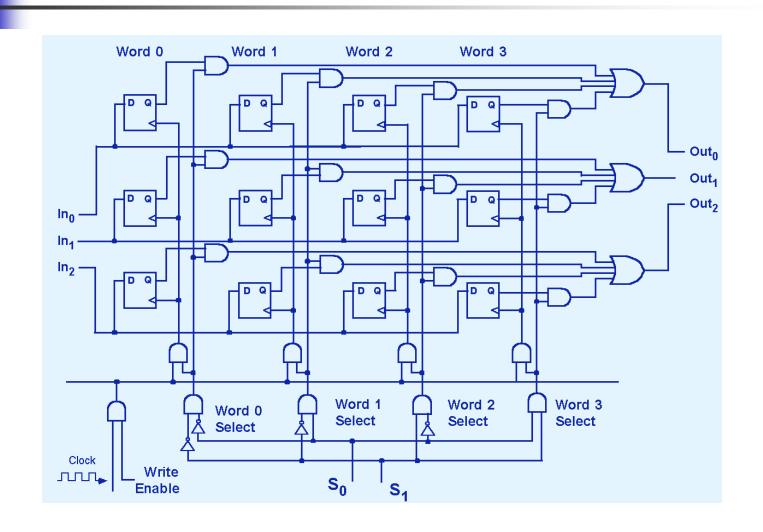

#### SEQUENTIAL CIRCUITS: FOUR BIT REGISTER

This illustration shows a 4-bit register consisting of D flip-flops. You will usually see its block diagram (below) instead.

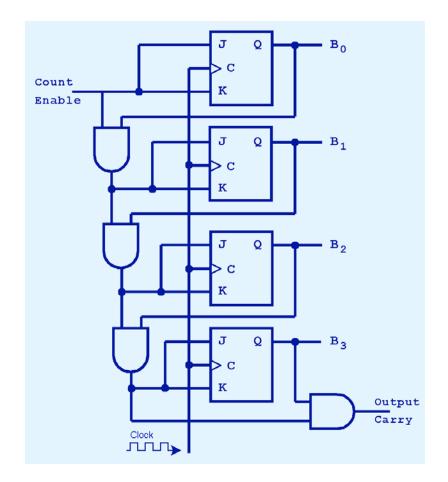

- A binary counter is another example of a sequential circuit.

- The low-order bit is complemented at each clock pulse.

- Whenever it changes from 0 to 1, the next bit is complemented, and so on through the other flip-flops.

# DIGITAL DESIGN: PART ONE

- We have seen digital circuits from two points of view: digital analysis and digital synthesis.

- Digital analysis explores the relationship between a circuits inputs and its outputs.

- Digital synthesis creates logic diagrams using the values specified in a truth table.

- Digital systems designers must also be mindful of the physical behaviors of circuits to include minute propagation delays that occur between the time when a circuit's inputs are energized and when the output is accurate and stable.

## **DIGITAL DESIGN: PART TWO**

- Digital designers rely on specialized software to create efficient circuits.

- Thus, software is an enabler for the construction of better hardware.

- Of course, software is in reality a collection of algorithms that could just as well be implemented in hardware.

- Recall the Principle of Equivalence of Hardware and Software.

# DIGITAL DESIGN: PART THREE

- When we need to implement a simple, specialized algorithm and its execution speed must be as fast as possible, a hardware solution is often preferred.

- This is the idea behind embedded systems, which are small special-purpose computers that we find in many everyday things.

- Embedded systems require special programming that demands an understanding of the operation of digital circuits, the basics of which you have learned in this LESSON.

# **BOOLEAN LOGIC: SUMMARY PART ONE**

- Computers are implementations of Boolean logic.

- Boolean functions are completely described by truth tables.

- Logic gates are small circuits that implement Boolean operators.

- The basic gates are AND, OR, and NOT.

- The XOR gate is very useful in parity checkers and adders.

- The "universal gates" are NOR, and NAND.

# **BOOLEAN LOGIC: SUMMARY PART TWO**

- Computer circuits consist of combinational logic circuits and sequential logic circuits.

- Combinational circuits produce outputs (almost) immediately when their inputs change.

- Sequential circuits require clocks to control their changes of state.

- The basic sequential circuit unit is the flip-flop: The behaviors of the SR, JK, and D flip-flops are the most important to know.

# **BOOLEAN LOGIC: SUMMARY PART THREE**

- The behavior of sequential circuits can be expressed using characteristic tables or through various finite state machines.

- Moore and Mealy machines are two finite state machines that model high-level circuit behavior.

- Algorithmic state machines are better than Moore and Mealy machines at expressing timing and complex signal interactions.